文章编号:1001-5078(2017)01-0062-05

• 红外材料与器件 •

# 一种基于 0.18 μm CMOS 工艺的高响应度 APD

王 巍,陈 丽,鲍孝圆,陈 婷,徐媛媛,王冠宇,唐政维 (重庆邮电大学光电工程学院/国际半导体学院,重庆 400065)

摘 要:设计了一种基于  $0.18~\mu m$  CMOS 工艺的高响应度雪崩光电二极管(APD)。该 APD 采用标准  $0.18~\mu m$  CMOS 工艺,设计了两个 P+/N 阱型 pn 节,形成两个雪崩区以产生雪崩倍增电流。雪崩区两侧使用 STI(浅沟道隔离)结构形成保护环,有效地抑制了 APD 的边缘击穿;并且新增加一个深 N 阱结构,使载流子在扩散到衬底之前被大量吸收,屏蔽了衬底吸收载流子产生的噪声,用以提高器件的响应度。通过理论分析,确定本文所设计的 CMOS – APD 器件光窗口面积为  $10~\mu m \times 10~\mu m$ ,并得到了器件其他的结构和工艺参数。仿真结果表明:APD 工作在 480~nm 波长的光照时,量子效率达到最高 90% 以上。在加反向偏压 -15~V 时,雪崩增益为 72,此时响应度可达到 2.96~A/W,3 dB 带宽为 4.8~GHz。

关键词:CMOS - APD;雪崩增益;响应度;带宽

中图分类号: TN364. 2 文献标识码: A DOI: 10.3969/j. issn. 1001-5078. 2017. 01.012

## High responsivity APD based on 0.18 µm CMOS technology

WANG Wei, CHEN Li, BAO Xiao-yuan, CHEN Ting, XU Yuan-yuan, WANG Guan-yu, TANG Zheng-wei (College of Electronics Engineering, Chongqing University of Posts and Telecommunications, Chongqing 400065, China)

Abstract: A high responsivity APD based on 0.18  $\mu m$  complementary metal-oxide-semiconductor (CMOS) process is designed. With the standard 0.18  $\mu m$  CMOS technology, two P+/N-well type pn junctions are designed to form two avalanche regions in order to produce avalanche multiplication current, and the guard-ring structure is formed with STI (Shallow Trench Isolation) structure on both sides of the avalanche region, which restrains the edge-breakdown effectively. A deep N-well structure has been applied in the APD to absorb a large number of carriers before they spread to the substrate, which screened the excessed noise and improved the responsivity of the device. Though theoretical analysis, the optical window area is 10  $\mu$ m × 10  $\mu$ m, other structure and process parameters of the CMOS-APD are also confirmed. The simulation results show that at wavelength of 480 nm, the quantum efficiency reaches up to 90%. The avalanche gain is about 72, the responsivity is 2.96 A/W and 3 dB bandwidth is about 4.8 GHz when the bias voltage is -15 V.

Key words: CMOS-APD; avalanche gain; responsivity; bandwidth

## 1 引 言

雪崩光电二极管(APD)作为一种光电转换器件,具有内部增益大、体积小、工作电压低等优点,近年来成为了光通信领域,尤其是850 nm 短距离光通

信系统的研究热点<sup>[1]</sup>。而基于 CMOS 工艺的 APD 采用 Si 作为材料,Si 中的电子和空穴碰撞离化率差值大,具有高增益、低噪声,且稳定性好,并且易于与后续放大电路集成,已经广泛应用于光通信系统和

光互联设备中[2]。

作为光电转换器件, CMOS - APD 器件最重要 的指标之一就是响应度,表征 APD 器件将光转换成 电流的能力。近年来,国内外学者对 CMOS - APD 进行了一系列研究。2012年, T. Shimotor [3] 提出了 一种 APD 结构,采用 0.18 μm CMOS 工艺,响应度 达到 2.61 A/W, 带宽为 300 MHz; 2013 年, K. livama<sup>[4]</sup> 采用 0.18 μm CMOS 工艺,设计出了带宽达到 10 GHz 的 APD, 其响应度只有 0.1 A/W; 2015 年, 本课题组[5]提出一种高带宽 NP 型 APD,带宽达到 8.6GHz,但响应度只有 0.47 A/W。从这些数据可 以看出响应度和带宽是两个相互制约的参量,但这 并不表示无法对二者进行折衷, M. Atef<sup>[1]</sup>等人于 2013 年设计了一种雪崩双光电二极管(ADPD),得 到了响应度达到 2.04 A/W, 带宽为 1.4 GHz/s 的 APD,在提高响应度的同时得到了比较宽的带宽。 本文基于这一出发点,通过定性分析载流子浓度、耗 尽区宽度、光窗口面积、深N阱深度等因素对带宽 和响应度的影响,设计了一种高响应度高带宽的 CMOS - APD

## 2 APD 的器件结构设计

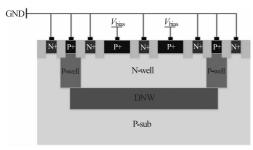

图1是本文基于 0.18 μm CMOS 工艺设计的 APD 的结构。以文献[6]提出的空穴注入型 APD 为基础,提出了一种新的 CMOS – APD 结构。首先,在此基础上增加了一个深 N 阱结构,用来屏蔽衬底噪声,然后根据文献[7]中的分析,确定了光窗口面积为 10 μm×10 μm。根据文献[8]对不同的 P 阱、N 阱、STI 宽度和掺杂浓度对带宽和电流的分析,结合文献[5],确定的 APD 结构,如图 1 所示。

图 1 一种新的 APD 结构

Fig. 1 The structure of a new APD

该 APD 为 P + / N - well / DNW / P - sub 型结构。光从器件的顶部入射,雪崩区由 P + / N 阱结构的 pn 结形成,采用 P + 离子注入和 N 型扩散工艺, P + 接阴极,从而使 pn 结反偏,为产生雪崩效应提供条件,并在其两端采用 STI 工艺形成保护环,提高器件耐压性,从而一定程度上提高带宽;深 N 阱采用 N

型离子扩散形成,其所接电极和衬底短接,可以阻止载流子扩散到 P 衬底产生噪声,提高响应度。

器件部分参数在表 1 中给出。P+ 区采用离子注入形成高掺杂的 P 区,浓度为  $1 \times 10^{19}$  ,N 阱采用扩散工艺,浓度为  $1 \times 10^{17}$  ,形成大的浓度差可以产生较大的电场( $6.77 \times 10^5$  V/cm),使载流子高度集中,从而发生雪崩效应使电流倍增;深 N 阱的掺杂浓度高于 P 衬底,防止了光生载流子扩散到衬底;由于工艺限制,P+ 和 N+ 区的深度设置为  $0.3~\mu m$  ( $0.18~\mu m$  CMOS 工艺对 STI 的深度要求最深为  $0.5~\mu m$ )。深 N 阱结构的深度为  $2.5~\mu m$ ,比较深的轻掺杂深 N 阱防止了较长波长的光在 Si 中的穿透深度很深而在衬底产生扩散电流,从而减少噪声。

表 1 APD 的部分工艺参数

Tab. 1 Part of the process parameters of APD

| layer    | Doping/cm <sup>-3</sup> | Depth∕µm |  |

|----------|-------------------------|----------|--|

| P – sub  | 1 × 10 <sup>15</sup>    | 4        |  |

| P – well | 1 × 10 <sup>17</sup>    | 2        |  |

| N – well | 1 × 10 <sup>17</sup>    | 2        |  |

| DNW      | 5 × 10 <sup>16</sup>    | 2. 5     |  |

| P +      | 5 × 10 <sup>19</sup>    | 0.3      |  |

| N +      | 5 × 10 <sup>19</sup>    | 0.3      |  |

## 3 APD 器件性能分析

## 3.1 *I-V*特性

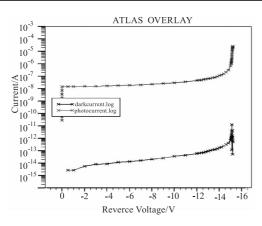

图 2 为在光波长为 480 nm,光强为 1 W/cm² 的条件下,本文所设计的 CMOS – APD 的 I-V 特性曲线。从图 2 中可以看出,暗电流在零偏时约为  $3 \times 10^{-15}$  A,当反偏电压超过 – 14 V 时,电流开始大幅度的增加,雪崩击穿电压大约在 – 15.4 V。在光照条件下,反偏电压为 0 V 时,光电流约为  $2 \times 10^{-8}$  A,反偏电压在 – 10 V 以下时,光电流几乎不变,而当加到 – 14 V 以上时,光电流开始快速增加,在 V=-15.4 V 时发生了雪崩击穿,雪崩击穿发生在 P+ 区和 N 阱之间的接触面,耗尽区的宽度可以通过式 (1)计算得出:

$$w = \left[\frac{2\varepsilon_s(V_{bi} + V_R)}{e} \left(\frac{N_a + N_d}{N_s N_s}\right)\right]^{\frac{1}{2}}$$

(1)

式中,  $V_R$  为外加电压;  $V_{bi}$  为 pn 结的内建电势(远小于外加电压,计算时可以忽略不计)带入 N + 和 P + 浓度计算得耗尽区深度约为 0.4  $\mu$ m。与文献[9]中的击穿电压(约 7 V)相比要大一些,这是因为采用了 STI 做保护环,允许器件工作在更高的偏压下。

图 2 APD 的 I - V 特性

Fig. 2 Current-Voltage characteristic curve of APD

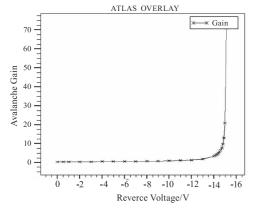

图 3 给出了在反偏电压下的雪崩增益,雪崩增益可以表示为:

$$M = \frac{I(V) - I_d(V)}{I(0) - I_d(0)} \tag{2}$$

式中,I(V) 和 I(0) 分别表示加偏压和 0 偏时对应的光电流; $I_a(V)$  和  $I_a(0)$  别表示加偏压和 0 偏时对应的暗电流。从图 3 中可以看出,当加偏压在 – 14 V 以上时,增益开始剧烈增长,此时产生了雪崩效应,在雪崩区大量产生电子,导致电流剧增。从图 3 中看出,当偏压加到 – 15 V 时,雪崩增益达到了约 72。

图 3 APD 的电压 - 增益曲线

Fig. 3 Voltage-Gain characteristic curve of APD

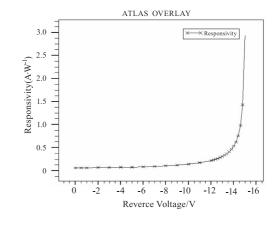

## 3.2 响应度

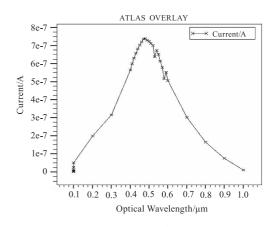

图 4 给出了不同波长的光谱响应,从图中可看出,光谱响应范围为 0.1 ~ 1.0 μm。由功率定义的响应度,其表达式如式(3):

$$R = \frac{I_p}{P_{out}} = \frac{\eta q}{h\nu} \tag{3}$$

其中, $I_p$  表示光电流与暗电流的差; $P_{opt}$ 表示入射光功率。从微观上来说,响应度主要受到光电流、暗电流(噪声电流)和量子效率的影响,从宏观上来看,入射光波长、N 阱深度、深 N 阱深度和浓度都会对

其有影响。提高响应度的方法有很多种, Kazuaki Maekita<sup>[10]</sup>提出加入一个深的 N 型埋层可以使载流 子在扩散到衬底之前被大量吸收,提高响应度;周 翔<sup>[11]</sup>提出使 APD 工作与最佳增益点并提高性噪比可以获得高响应度。

图 4 APD 的光谱响应 Fig. 4 Spectral Response of APD

从图 5 中可以看出,当偏置电压为 0 时,响应度约为 0.01 A/W,当偏置电压加到 – 14 V 时,响应度约为 0.4 A/W,当偏置电压加到 – 15 V 时,由于产生了雪崩增益,响应度也得到了很大的提升,约为 2.96 A/W。这与 Myung-Jae Lee<sup>[7]</sup>得到的 0.48 A/W响应度和 Zi-Ying Li<sup>[12]</sup>得到的 1.24 A/W 相比,响应度相比有了很大的提升。这是因为加入了深 N 阱结构,深 N 阱能提高不同模块间的电隔离,当载流子流经 P+和 N 阱到达深 N 阱区域时,由于深 N 阱的掺杂浓度大于 P 衬底的掺杂浓度,使得其阻止了衬底上光生载流子的缓慢扩散,能屏蔽噪声并提高响应度<sup>[7]</sup>。

图 5 APD 的电压 - 响应度曲线

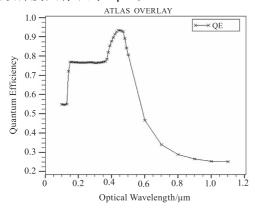

Fig. 5 Voltage-Responsivity characteristic curve of APD 量子效率表示一定数量特定波长的光量子被半

导体吸收时,能够形成光电流的数目,表示为:

$$\eta = \frac{I_{APD}/e}{P/hv} \tag{4}$$

图 6 给出了不同波长的量子效率。从图 4 和图 6 可以看出,波长为 480 nm 的波长,光谱响应度最好,量子效率也最高,对于此器件来说,短波长的光产生的电流会更大一些,这是因为 Si 对不同的波长的光的吸收深度不一样,对 850 nm 波长的光而言,吸收深度可以达到 16.5  $\mu$ m<sup>[1]</sup>,而对 400 nm 波长光的吸收深度只有不到 1  $\mu$ m。

图 6 APD 的量子效率 Fig. 6 Quantum Efficiency of APD

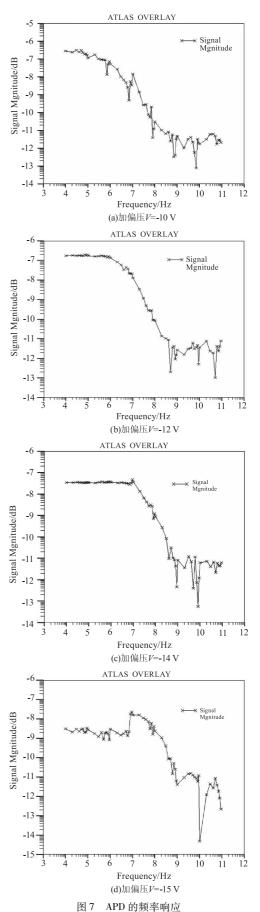

## 3.3 频率响应

频率响应是 APD 性能的一个重要指标,从器件的频率响应曲线可以直观看出 3 dB 带宽。APD 的带宽可以用式(5)表示:

$$BW = \frac{1}{\sqrt{\left(\frac{2\pi}{\omega_{RC}}\right)^2 + \left(\frac{2\pi}{\omega_t}\right)^2}}$$

(5)

式中, $\omega_{RC}$  为 RC 时间常数, $\omega_{RC} = \frac{1}{C_d R_d}$ ,其中  $C_d$  表示结电容; $R_d$  表示体电阻; $\omega_t$  表示载流子渡越时间的频率。从微观来说来说,影响带宽的因素主要有:载流子的输运时间和器件的 RC 常数。从宏观来说,增大带宽的方法有很多种,Myung-Jae Lee<sup>[7]</sup>通过分析不同的光窗口面积,发现窗口面积越小,耗尽区的电容就越小,器件的频率响应越好,相应的 3dB 带宽也就越大;Koichi Iiyama<sup>[4]</sup>提到,减小电极间的间隔能够减少载流子的渡越时间,增大带宽。

设计的 CMOS-APD 采用了 10 μm×10 μm 的 光窗口面积,一定程度上减小了 pn 结的结电容 从而增大了 RC 时间常数;而增加的深 N 阱的浓度比衬底的浓度大,增大了载流子的漂移和扩散速度从而减小了载流子渡越时间,增大了带宽。图 7 给出了 480 nm 的光在加不同偏压下的频率响应。

Fig. 7 Frequency response of APD

从图 7 中可以看出, 当加偏压 V = -10 V 时, 得到的 3 dB 带宽约为 30 MHz; 当加偏压 V = -12 V 时, 得到的 3 dB 带宽约为 90 MHz; 当加偏压 V = -14 V 时, 得到的 3 dB 带宽约为 300 MHz; 当加偏压 V = -15 V时, 得到的 3 dB 带宽约为 4.8 GHz。由此得出结论, APD 器件上加的反向偏压越大, 得到的 3 dB 带宽就越大, 这是因为当偏压增加时, 一方面电场增强, 载流子受到的漂移作用变大导致载流子渡越时间变小, 带宽变大 [1]; 另一方面, 雪崩增益变大, 带宽变大 [7]。而从理论上分析, 电压增大, pn 结的耗尽区宽度变大, 结电容变小, 带宽变大。其APD 性能与其他方法设计的 APD 比较如表 2 所示。

表 2 CMOS 工艺下的 APD 的性能比较 Tab. 2 Comparison of CMOS-APD performance

| Ref  | 光窗口<br>面积/<br>μm² | 击穿<br>电压<br>/V | 3dB<br>带宽<br>/Hz | 雪崩 增益 | 响应度/<br>(A・W <sup>-1</sup> ) | 使用工艺<br>(CMOS) |

|------|-------------------|----------------|------------------|-------|------------------------------|----------------|

| [1]  | 30 × 30           | 10. 6          | 3. 2G            | _     | 2. 94                        | 40 nm          |

| [3]  | 20 × 20           | 9. 2           | 300M             | 36    | 2. 61                        | 0. 18 μm       |

| [4]  | 10 × 10           | 9. 1           | 10G              | _     | 0. 1                         | 0. 18 μm       |

| [13] | 20 × 20           | 9. 2           | 7G               | 86    | 0. 65                        | 0. 18 μm       |

| 本文   | 10 × 10           | 15. 2          | 4. 8G            | 72    | 2. 96                        | 0. 18 μm       |

#### 4 结 论

本文设计了一种新型的 CMOS-APD 器件。该结构光窗口面积为  $10~\mu m \times 10~\mu m$ ,在 pn 结正下方增加了一个深 N 阱结构,并将深 N 阱和 P 衬底短接,阻止了载流子扩散到 P 衬底产生噪声,深 N 阱结构同时使得 RC 时间常数增加,载流子渡越时间减小,在提升了响应度的同时,一定程度上增加了带宽。器件仿真结果表明,器件反偏电压 V=-15~V 时,发生雪崩击穿,雪崩增益达到 72,响应度高达 2.96~A/W,3~dB~带宽约为 <math>4.8~GHz。

#### 参考文献:

- [1] M Atef, et al. Avalanche double photodiode in 40 nm standard CMOS technology[J]. IEEE Journal of Quantum Electronics, 2013, 49(3):350 356.

- [2] B Ciftcioglu, et al. 3GHz silicon photodiodes integrated in a 0. 18 µm CMOS technology [J]. Photonics Technology Letters IEEE, 2008, 20(24):2069 2071.

- [3] T Shimotori, K Maekita, T Maruyama, et al. Characterization of APDs fabricated by 0.18 µm CMOS process in blue wavelength region [C]. IEEE Opto-Electronics and Communications Conference (OECC), 2012;509 510.

- [4] K Iiyama, T Shimotori, R Gyobu, et al. 10 GHz bandwidth of Si avalanche photodiode fabricated by standard 0. 18 µm CMOS process [C]. OECC, 2014;243 244.

- [5] WANG Wei, WANG Chuan, YYAN Linshu, et al. NP type CMOS APD with high frequency bandwidth [J]. Infrared and Laser Engineering, 2015, 44(2):699 - 704. (in Chinese)

- 王巍, 王川, 颜琳淑, 等. 一种高带宽 NP 型 CMOS APD 的研究[J]. 红外与激光工程, 2015, 44(2): 699 704.

- [6] K Iiyama, H Takamatsu, T Maruyama, et al. Hole-Injection-Type and electron-Injection-Type silicon avalanche photodiodes fabricated by standard 0. 18μm CMOS process[J]. IEEE Photonics Technology Letters, 2010, 22 (12):932-934.

- [7] M J Lee, W Y Choi, et al. Area-dependent photodetection frequency response characterization of silicon avalanche photo-detectors fabricated with standard CMOS technology [J]. IEEE Transactions on Electron Devices, 2013, 60 (60):998-1004.

- [8] LIU Yuzhang. Photodetectors fabricated by standard silicon process technology [D]. National Central University, 2007. (in Chinese)

劉玉章. 短波長光通訊之矽標準製程光檢測器[D]. 國立中央大學,2007.

- [9] E R Moutaye, H Tap-Beteille, et al. Integration of CMOS avalanche photodiodes evaluation and comparison of their global performances [C]. IEEE Instrumentation and Measurement Technology Conference, 2010;1373 – 1376.

- [10] K Maekita, T Shimotori, T Maruyama, et al. GHz response of Si photodiodes fabricated with 0.35 µm Si BiCMOS technology [C]. IEEE 9th International Conference Group IV Photonics (GFP), 2012;267 269.

- [11] ZHOU Xiang, XU Mingyang, ZHANG Jiuming. Design and implementation of high sensitivity APD optical receiver [J]. Optical Communication Technology, 2015, 39(9): 30-32. (in Chinese) 周翔,徐明阳,张久明. 高灵敏度 APD 光接收机的设计与实现[J]. 光通信技术,2015,39(9):30-32.

- [12] Z Y Li, F P Chou, C W Wang, et al. A new 850nm lateral Si avalanche photodiode in standard CMOS technology [C]. IEEE OptoeElectronics and Communications Conference (OECC), 2011:479 – 480.

- [13] T Shimotori, K Maekita, R Gyobu, et al. Optimizing interdigital electrode spacing of CMOS APD for 10 Gb/s application [C]. IEEE OptoElectronics and Communications Conference held jointly with 2013 International Conference on Photonics in Switching, 2013:1-2.