文章编号:1001-5078(2010)02-0187-05

· 光电技术与系统 ·

# 基于多波束风场位移测量法的高速数据采集和处理系统设计

周立敏1,蒋亚东1,眭晓林2

(1. 电子科技大学光电信息学院 电子薄膜与集成器件国家重点实验室,四川 成都 610054;2. 华北光电技术研究所,北京 100015)

摘 要:为实现对风场的实时监控,多波束风场位移测量系统对数据采集系统提出了很高的要求。针对实际需求,设计了实现高速数据缓存和传输控制的 FPGA 芯片,主要包括 PLL 时钟管理模块、前级 FIFO 缓冲模块、后级双口 RAM 存储模块以及 FIFO 和 RAM 的读写控制模块等,很好地完成了数据的缓存和异步读取,并且极大简化了 A/D 芯片接口电路结构和印制电路板设计的复杂性。在开发环境 Quartus II 6.1 中对设计的各个模块分别进行了综合和仿真,仿真结果表明各模块均达到了设计要求。风场位移测量系统成功地对实地风场进行了测量,结果表明高速数据采集系统能够有效地检测出风场中不同距离处的散射回波信号,并据此计算出风速以及风向。

关键词:风场测量;位移;高速数据采集;FPGA

中图分类号:TP274<sup>+</sup>.2 文献标识码:B

## Design about sampling and processing system of high-speed data for multi-laser beams measuring system of wind fields

ZHOU Li-min<sup>1</sup>, JIANG Ya-dong<sup>1</sup>, SUI Xiao-lin<sup>2</sup>

(1. State Key Laboratory of Thin Solid Film and Integrated Devices, School of Optoelectronic Information, University of Electronic Science and Technology of China, Chengdu 610054, China; 2. North China Research Institute of Electronic and Optic, Beijing 100015, China)

Abstract: The high demand of data acquisition system was proposed to realize the real-time monitoring of wind fields in the multi-beam displacement measurement of wind field system. In this paper, the FPGA chips was well designed to achieve cache and transmission control of high-speed data to meet the actual demand, including PLL clock management module, the preceding stage of FIFO buffer module, the rear stage of dual-port RAM memory modules and the reading and writing control module of FIFO and RAM. It not only fulfilled caching and asynchronous data reading, but also greatly simplified the interface circuit structures of A/D chip and the design of printed circuit board. Synthesis and simulation of all modules was carried out using the program Quartus II 6.1. The result presented perfect satisfaction to the design requirements. The wind field was successfully measured by the displacement measuring system, which presented the high-speed data acquisition and processing system could effectively detect the echo signal in different distance. Therefore, we can calculate the wind speed and get the wind direction according to the detected signals.

Key words: wind field measurement; displacement; high-speed data acquisition; FPGA

## 1 引言

大气风场与人类的生活息息相关,而相关的灾 害性台风每年造成数以亿计的巨大损失,所以对研 究全球气候变化和实现实时天气预报具有重大意 义[1-3]:此外,低空风切变,也对航空航天安全构成 严重威胁。因此,准确、及时、便利的大气风场监测 对于提高风暴预报的准确性、改进天气研究模型非 常重要。当前,常见的风速测量手段包括气象气球、 声达探测器、微波测风雷达等,但都存在很多问题, 诸如使用不便、精度不高、实时性差、分辨率低等。 近年来,激光测风技术由于具有测量速度快、机动性 高、快速、精度高等优点,越来越受到人们的广泛关 注。到目前为止,激光测风设备都是基于多普勒原 理的反射回波[4-5]实现的,其对激光的波长和频率 的稳定性要求高,且系统复杂、使用维护不便 等[6-8]。为实现对近距离风场的实时监控,我们设 计了一种采用多光束测量风场位移的新型激光测风 仪,通过对激光的后向散射回波的强度进行数据采 集和分析,计算得到风速和风向。该测风仪具有结 构简单、适应性强的优点。

由于短时间内大气风场回波动态范围大,变化速度快,且回波信号信噪比较低,因此系统对数据采集系统提出了很高的要求。根据激光测风装置的工作参数确定了数据采集系统的采样频率为200 MHz,采样数据量为200点。为了缓解高速数据流对后续时序电路的压力以及防止数据丢失,必须对数据先进行缓存。本方案选择了基于FPGA的FIFO和双口RAM模块作为数据缓存器,很好地完成了数据的缓存和异步读取,并且极大简化了A/D芯片接口电路结构和印制电路板设计的复杂性。

## 2 高速数据采集系统设计及结果讨论

## 2.1 基于 FPGA 的缓存及控制电路

作为高速数据采集系统的核心功能模块,FPGA 承载了大部分的数字电路<sup>[9-11]</sup>。本设计中 FPGA 主要集成了 PLL 时钟管理模块、前级 FIFO 缓冲模块、后级双口 RAM 存储模块以及 FIFO 和 RAM 的读写控制模块等。本系统采用了 Altera 公司的 Cyclone - II 系列 FPGA"EP2C8Q208C8",开发环境为 Quartus II 6.1。由于使用硬件描述语言编写 FIFO 以及 RAM 模块比较复杂,且经综合后模块不稳定,因此采用 Quartus II 中提供的参数化宏功能模块(LPM),极大地提高了系统的设计效率和可靠性。

## 2.1.1 PLL 时钟管理模块

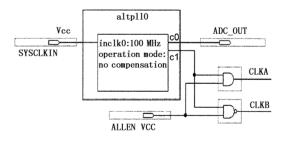

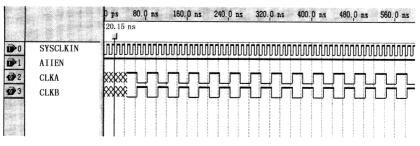

锁相环(phase lock loop, PLL)是一种模拟反馈 电路,其主要作用是使外部输入时钟的相位和频率 同步于内部参考时钟。通过 MegaWizard 调用 ALT-PLL 模块即可生成所需要的锁相环。本设计中采用 的PLL模块如图1所示。其中,SYSCLKIN由外部 100 MHz 晶振提供,作为 PLL 模块的输入信号。 ADC OUT 经 PLL 倍频后得到 200 MHz 的频率作为 ADC08200 的采样时钟。CLKA 和 CLKB 是 SY-SCLKIN 经 PLL 同步后经过与门和与非门产生的两 个相位相反的 100 MHz 时钟,分别提供给前级两个 FIFO 作为写时钟,同时 CLKA 也作为整个系统的全 局时钟,驱动全片的所有触发器和时序电路。AL-LEN 为全局使能信号,用于控制系统工作状态。为 减小信号到达各个时序元件(触发器)的时间偏斜, 时钟和复位信号采用 FPGA 内部的全局时钟网络实 现。PLL 模块时序仿真图如图 2 所示。

图 1 PLL 时钟管理模块示意图

图 2 PLL 时钟管理模块仿真时序图

#### 2.1.2 前级 FIFO 缓存模块

对于高采样频率带来的高速数据流,如果直接采用 FIFO 或 RAM 进行缓存,将对时序电路的实现造成很大困难。因此,本文采用了分时采集的方法,通过分别给两个前级 FIFO 提供相位相反的100 MHz 写时钟,分时写入 A/D 转换的数据,从而达到高速缓存的目的。

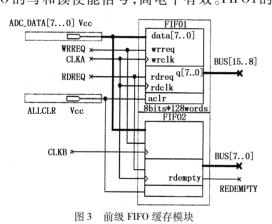

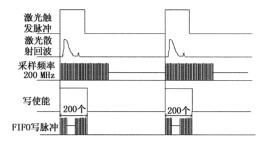

前级 FIFO 缓存模块由两个输入输出均为 8 位的 FIFO 组成,如图 3 所示,用于缓存 200 个(两个 FIFO 各 100 个) A/D 转换的数据,输出总线为 16 位,两个 FIFO 各占 8 位数据总线。ADC\_DATA[7..0]是 A/D 转换器的输出,作为两个 FIFO 模块的数据输入,CLKA 和 CLKB 由 FPGA 内部 PLL 模块产生,相位相差 180°,分别作为两个 FIFO 的写时钟信号,CLKA 还作为两个 FIFO 的读时钟信号。ALL-CLR 是两个 FIFO 的异步清零输入信号以及全局清零信号,高电平有效。WRREQ 和 RDREQ 分别是FIFO 的写和读使能信号,高电平有效。FIFO1 的数

据输出口 BMS[15..8]作为 16 位总线的低 8 位, FIFO<sub>2</sub> 的数据输出口 BMS[7..0]作为 16 位数据总线的高 8 位。FIFO 的读空信号 RDEMPTY 表示当前 FIFO 所存数据的深度,当 RDEMPTY 出现低电平时,表示此时 FIFO 中已写有数据,把它作为读数据控制模块的输入信号,这样可以在写数据的同时从 FIFO 中读出数据,提高效率。FIFO 缓存时序如图 4 所示。

图 4 FIFO 缓存时序示意图

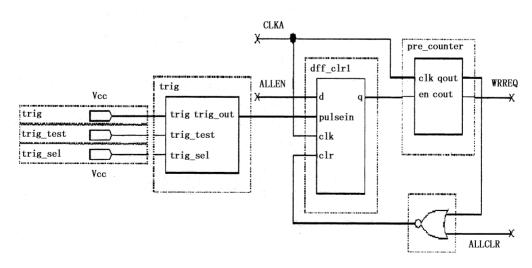

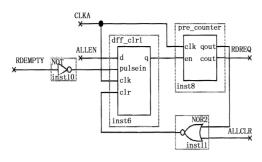

## 2.1.3 前级 FIFO 控制模块

前级 FIFO 控制模块由触发选择模块、写数据控制和读数据控制三个子模块组成,如图 5、图 6 所示。触发选择模块相当于选通开关, trig\_oμt 为 FIFO 写控制的触发信号, trig\_sel 由单片机控制选择。当 trig\_sel 为高电平时,触发信号来源于激光主波脉冲,此时高速数据采集系统的启动完全取决于前端脉冲激光的发射时间;当 trig\_sel 为低电平时,触发信号来源于单片机控制系统模拟产生的触发脉冲信号 trig\_test,此时数据采集的启动可以通过计算机发送相应的控制命令来完成。trig\_test 主要用于前期测试数据采集系统是否正常工作。

图 5 FIFO 写控制模块

图 6 FIFO 读控制模块

写控制模块限定前级 FIFO 写 AD 的数据个数为 200,即每个 FIFO 各写人 100 个数据。触发信号 trig(上升沿有效)一旦来临,D 触发器将 d 端的高电平(全局使能 ALLEN)送至 pre\_counter 模块的 en端,在 CLKA 的时钟下启动计数,在计数过程中 cout端输出高电平以使 FIFO 写使能有效,计满 100 个脉冲后,pre\_counter 模块 qout端输出高电平,将 D 触发器复位,同时 cout端输出低电平,停止向 FIFO 中写入数据。复位完成后,写数据计数模块停止计数,等待下一次触发信号,一旦触发信号再次产生,将立即重复以上操作。

读数据控制模块基本与写数据控制模块相同, 只是 D 触发器的触发信号由 RDEMPTY 反向得到, 即当 FIFO 中有数据时 pre\_counter 就开始计数,使 FIFO读使能信号 RDREQ有效,这样对 FIFO的写 数和读数可以同时进行。值得注意的是,本系统采用全局时钟同步各个模块,且为确保正确采样,trig信号和 RDEMPTY 信号的变化频率不能高于 CLKA的时钟频率。

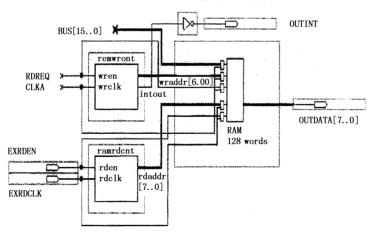

#### 2.1.4 后级双口 RAM 存储模块

后级双口 RAM 的作用是实时存储从 FIFO 中读出的数据,以方便外部的控制器(单片机)异 步读取数据。如图 7 所示, BUS [15..0]作为 RAM 的输入, ramwrent 和 ramrdent 模块分别是双 口RAM写地址和读地址计数器。CLKA作为 RAM 的写时钟, 当前级 FIFO 的读控制模块输出 读使能信号 RDREQ(高电平)时,双口 RAM 的写 地址计数器开始计数,同时向 RAM 中写入数据。 一旦计满100个数(写数据总线为16位,相当于 200 个 8 位数据),即产生一个 OMTINT 信号(高 电平),通知外部控制单元来读取 RAM 中的数 据。EXRDEN 和 EXRDCLK 分别为外部读使能 信号和外部读数时钟。当外部控制器收到 FPGA 给出的中断信号,首先应置 EXRDEN 为高电平, 然后才能开始读数,由于这里 FPGA 与外部控制 器连接的数据总线为8位,因此双口 RAM 读地 址计数控制器需计满 200 个数才能将 RAM 中的 数据全部读出。

图 7 后级双口 RAM 存储模块

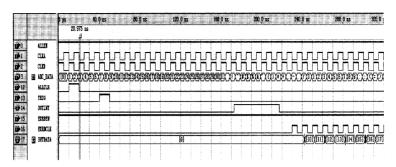

## 2.2 FPGA 综合仿真与风场检测

根据上述设计思路,在 Altera 公司的开发环境Quartus II 6.1 中针对 Cyclone – II 系列 FPGA 芯片EP2C8Q208C8 进行了综合和仿真,其时序结果如图8 所示。其中 CLKA 和 CLKB 为 100 MHz 时钟,相位相反,ADC\_DATA 总线数据速率为 200 MHz。为了使结果更直观,在仿真时前级 FIFO 和后级 RAM的读写数据个数改为了 16 个,即前级两个 FIFO 各

存储 8 个数据。从图中可以看出,输出数据(OMT-DATA)为 10~17,即 TRIG 信号来临时后,ADC\_DA-TA 总线上的数据开始写入前级 FIFO。这里没有对 FIFO 的 RDEMPTY 输出信号做仿真,但是可以看到 OMTINT 输出了高电平,即当存储在 RAM 中的数据 为一定个数时,产生了外部中断信号。通过加入外 部使能信号和外部读数时钟仿真信号,可以看到从 双口 RAM 中读出的数据是正确的。

图 8 FPGA 缓存时序仿真图

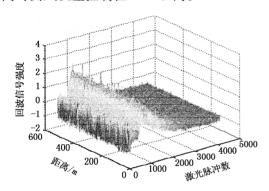

风场位移测量系统已成功研制成收发一体化系统,并进行了200 m 范围内风场测量实验。本系统中使用的激光脉冲频率为20 Hz。每一个激光脉冲发射时,触发高速数据采集系统对信号进行采样,将各时刻的信号大小记录下来。系统在一段时间内,记录下多个脉冲下各个时刻的回波信号,即可得到不同距离(时刻)和激光脉冲下接收到的散射回波信号强度分布,如图9所示。实验结果表明,本系统能够有效地检测出不同距离处的风场的风速以及风向,同时测风误差控制在10%以内。

图 9 不同距离和激光脉冲下接收到的散射回波信号 归一化强度图

## 3 结 论

本文成功地设计了工程上实用的高速数据采集系统的 FPGA 芯片,达到了基于多光束激光后向散射的风场位移测量系统对风场实施实时监控的测量要求。在200 m 范围内采用风场位移测量系统成功地进行了风场测量,测量误差小于10%。结果证明FPGA 很好地完成了高速数据采集系统中对数据的缓存和传输控制,为风场位移测量系统的实现提供了坚实有力的硬件基础。

#### 参考文献:

- [1] Atlas R. The potential impact of space-based lidar winds on weather prediction[C]. Update on Recent Experiments at the Nasa Dao, Oxnard, CA, 2003:17 19.

- [2] Htlffaker R M, Lawrence T R, et al. Feasibility studies for a global wind measuring satellite system: A nalysis of simulated performance [J]. Appl. Opt, 1984, 23: 2532 2536.

- [3] Negra N B, Holmstrm O, et al. Aspects of relevance in offshore wind farm reliability assessment [J]. IEEE Trans. Energy Conv., 2007, 22:159 – 166.

- [4] Dobler J T, Gentry B M, Reagan J A. Doppler lidar using aerosol backscatter and a frequency agile laser transmitter for profiling atmospheric winds in the planetary boundary layer [J]. IEEE, 2002, 5:2687 2689.

- [5] Matthew J M, Wilbert R S, et al. Incoherent Doppler LI-DAR for continuous measurement of wind and aerosol profiles [C]. Piscataway NJ, 1994, 2:934 – 936.

- [6] Deepak K D, Veerabuthiran S, et al. Optimization of Doppler lidar system parameters for the measurement of atmospheric wind speed[J]. SPIE, 2006, 6409:1-7.

- [7] Jack A McKay, David J Rees. Design of a direct-detection Doppler wind lidar for spaceflight [J]. SPIE, 1998, 3494: 250 - 258.

- [8] Leland R P. Requirements and models for adaptive optics in coherent LIDAR wind measurements [J]. IEEE, 1992, 4:3540-3541.

- [9] 汤少维. 基于 FPGA 控制的高速数据采集系统设计与 实现[D]. 成都:电子科技大学,2007.

- [10] 于恒,肇云波. 基于 FPGA 高速数据采集的解决方案 [J]. 现代电子技术,2007,5:145-151.

- [11] 梁书豪. C8051F020MCU 在高速数据采集系统中的应用[J]. 电气应用,2007,12:40-44.