文章编号:1001-5078(2014)02-0204-03

·图像与信号处理。

# 一种基于 FPGA 的红外探测器模拟器的设计

董常军,王朝林(中国空空导弹研究院,河南洛阳471009)

摘 要:红外探测器模拟器可以在多个场合代替探测器使用,可以减少价格高昂的红外探测器不必要的损伤,因此具有很高的实用价值。本文介绍了一种以 Xilinx 公司 FPGA 芯片作为核心,配以 D/A 转换器的红外探测器模拟器的设计方法,给出了 FPGA 内部的详细设计,并对模数混合电路制版时的注意要点进行介绍。

关键词: 红外探测器; FPGA; 图像生成; 时序控制

中图分类号:TN216 文献标识码:A **DOI**:10.3969/j.issn.1001-5078.2014.02.021

# Design of infrared focal plane array detector simulator based on FPGA

DONG Chang-jun, WANG Chao-lin (China Airborne missile academy, Luoyang 471009, China)

Abstract: The infrared detector simulator can replace the detector on many occasions, it can avoid unnecessary damage of the high cost infrared detectors, so it is of high practical value. Infrared detector simulator design is described, the simulator uses a Xilinx FPGA chip as the core together with the D/A converter. The detailed design of the FPGA is given, the keys of the hybrid circuit design and the layout are introduced.

Key words: infrared detectors; FPGA; image generation; timing control

#### 1 引言

在进行红外成像制导系统的调试与环境试验过程中,需要红外焦平面探测器提供图像信息输入。对红外探测器长时间通电工作和多次重复进行上电、下电操作,会对红外探测器产生损伤,直接影响探测器的性能和使用寿命。因此有必要研制一种红外探测器模拟器,可以模拟红外探测器的输出,生成满足红外制导系统调试时需要的图像,从而减少红外探测器的通电时间和使用次数,延长其使用寿命。本文提出了一种基于 FPGA 的红外探测器模拟的设计方法,单板即可模拟主流红外焦平面探测器的基本功能。本红外探测器模拟器对缩短红外制导系统研制周期、降低成本以及提高效费比具有重要的作用,符合智能化、灵活、通用性的军事电子装备的发展潮流,具有很强

的实用价值。

#### 2 系统总体设计

#### 2.1 系统组成

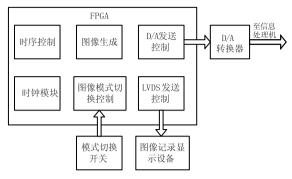

整个系统由单块电路板实现。模式切换开关控制 FPGA 生成的图像模式和模拟的探测器时序;FP-GA 在模式开关的控制下,模拟不同时序红外探测器及不同红外场景图像生成功能,并根据 D/A 时序要求把数据发送给 D/A 转换器进行转换;通过LVDS 接口将图像送到记录设备用于调试与记录分析。D/A 芯片接收 FPGA 发送的数字图像并转换成模拟信号后送给后端的红外成像信息处理系统。红外探测器模拟器系统结构如图 1 所示。

作者简介:董常军(1981 - ),男,硕士,工程师,研究方向为红外信息处理与 FPGA 设计。E-mail;changjund@ 163. com

收稿日期:2013-06-27;修订日期:2013-07-09

图1 系统结构框图

#### 2.2 FPGA 内部设计

FPGA 是整个系统的核心部件,完成的功能有:时序控制、图像生成、图像模式切换选择、LVDS 数据发送控制等。

#### 2.2.1 时序控制模块

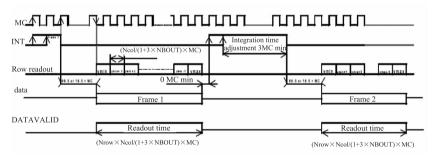

典型红外探测器的时序图如图 2 所示。时序控制模块的功能是模拟探测器的时序,生成相应的帧信号、行信号。探测器主时钟由 FPGA 系统时钟分频得到。整个模块的设计基于一个计数长度可调的计数器,根据计数器的计数结果输出行列时序信号,从而产生行列地址信号和帧信号。在该模块的设计中,时序电路的主要参数如帧频、主时钟频率、积分时间下降沿到图像输出的延迟时间、探测器有效行列数等都可以根据图像模式切换控制模块的输入进行配置,从而实现模拟多种探测器。积分时间信号由后端的红外成像信息处理系统给出,并作为时序控制模块计数器的复位信号,从而保证红外探测器模拟器的时序与后端红外成像信息系统的时序始终保持一致。

图 2 典型探测器时序图

#### 2.2.2 图像模式切换控制模块

为了提高红外探测器模拟器系统的适应性,模拟不同探测器的不同时序,设计了图像模式切换控制模块。不同时序的主要区别是帧频、主时钟频率、积分时间长度、积分时间下降沿到数据输出中间等待时间、有效图像行列数(128×128或是320×256)、行正程行逆程时间、探测器模拟数据输出电平高低等。此模块的设计有两部分,一是外部的选

择控制信号,由一个8位的拨码开关实现,高4位和低4位用来分别进行时序选择和图像内容选择。拨码开关高4位和时序选择器相联,可以译出16种状态,区分16种时序;低4位和图像内容选择器相联,也可以译出16种状态,区分16种不同图像内容。第二部分设计是FPGA内部的选择控制电路,由一个4位译码器和16选1选择器组成。拨码开关拨到不同的位置,就可以选择不同的配置参数,即可实现不同时序、不同图像内容的切换,高效而简洁。

#### 2.2.3 图像生成模块

为了验证红外图像处理软件和制导系统的功能, 红外模拟探测器除了能给出一个稳定的目标及背景图 像之外,还要可以模拟一个或多个目标在一定背景条 件下的简单运动的图像,以此来验证图像截获和跟踪 算法,以及制导回路的整体功能,因此设计了图像生成 模块。因为图像生成和探测器时序密切相关,因此图 像生成模块和时序控制电路一起,受图像模式切换控 制模块控制。在此模块中,图像的主要参数:目标个 数、目标位置、目标大小、目标灰度、背景灰度、目标的 运动速度和轨迹等也都设计成可配置参数模式。根 据模式切换控制模块的选择,选择不同的目标参数, 就可以实现完成目标位置、大小、灰度及运动特征等 的设置,根据时序控制电路产生的图像行列地址信息 在相应的位置根据需要进行赋值处理即可。

#### 2.2.4 D/A 控制模块

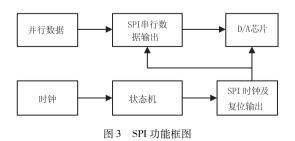

FPGA 通过 SPI 串口与 D/A 转换芯片 MAX5201 进行通信。MAX5201 有四个控制输入

端:SCLK(时钟)、CS(单片选,低有效)、DIN(数据输入)、LDAC(多片选,低有效),由于本设计只有一片 DA 芯片,因此设计片选信号(LDAC)始终为低,SCLK信号始终保持,由片选通 CS信号控制操作。SPI的时序要求参见 MAX5201器件手册。

SPI 串口实现的功能框图如图 3 所示。

### 2.2.5 LVDS 传输控制模块

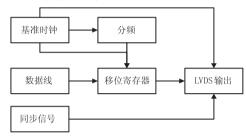

为了方便系统调试过程中图像数据的分析,设计了 LVDS 传输电路,将图像数据传输给外置的图像采集记录设备。LVDS 传输电路的设计,参考 Xilinx 公司参考设计手册 XAPP233 的设计方法,16 位数据通过并转串移位寄存器进行移位处理,通过DDR,将偶数位锁存于传送时钟的上升沿,奇数位锁存于传送时钟的下降沿。

LVDS 电路功能框图如图 4 所示。

图 4 LVDS 功能框图

#### 3 PCB 制版与模拟电路设计

本系统虽然采用单板方式实现,系统并不复杂, 但由于采用了 FPGA 及高速 D/A,也是一个数模混 合电路,并且频率也较高,因此,在进行 PCB 布线的 时候,也有很多需要特别注意的地方。首先,在元器 件布局时,考虑到将模拟电路器件和数字电路器件 分开放置,模拟信号在在模拟区内布线,数字信号在 数字电路区域布线,这样可以避免数字信号返回电 流流入模拟信号的地。对于 D/A 转换后的模拟信 号,考虑到噪声及干扰的影响,可以用一个 AD8138 进行差分化处理。高频的数字信号线尽可能的远离 敏感的模拟电路器件。对于 D/A、晶振这样的混合 器件,器件内部同时有数字电路和模拟电路两部分。 推荐将 AGND 和 DGND 引脚在外部都连接到同一 低阻的模拟地平面,而且引线要尽量短,任何 DGND 额外的阻抗都会通过寄生电容将更多的数字噪声耦 合到器件内部的模拟电路中。这样会比把转换器件 的 DGND 管脚接到数字接地平面带来的干扰要小 得多。由于电容器的容抗与频率成反比,因此在信 号与地线之间并联电容可以起到对高频噪声的旁路 作用。一般旁路推荐使用 0.01 ~ 0.1 μF 的陶瓷片 电容,不仅能使芯片存储能量,提供和吸收该芯片的 电路关断瞬间的充放能量,还能旁路过滤掉该器件

的高频噪声成分。在电源输入端加上一个 10~100 μF 的电解电容,可以抑制电源的噪声干扰。使用电容器时应该注意电容的引线尽量短,即让电容尽可能地靠近芯片。

#### 4 结束语

该系统已经成功应用到某红外成像系统的研制中,有效降低了价格高昂的红外探测器的使用频率,取得了较好的经济效益。采用该设计的红外探测器模拟器具有结构简单、成本低、功耗低、体积小等诸多优点,在外围电路不作任何改动的情况下,仅通过外置拨码开关来就可以改变探测器模拟器的时序和图像内容,基本上能够模拟多个厂家生产的主流红外探测器。

## 参考文献:

- [1] Qin Jinming, Chen Baoguo. Design of a system for simulating readout sequence of infrared focal plane array detector [J]. Infrared, 2007, 28(12):1-5. (in chinese) 秦金明,陈宝国. 模拟红外焦平面探测器读出时序的系统设计[J]. 红外, 2007, 28(12):1-5.

- [2] Sui Xiubao, Chen Qian, Gu Guohua. Study on IR dummy detector [J]. Infrared Technology, 2007, 29(10):563-566. (in chinese) 隋修宝,陈钱,顾国华,等. 红外模拟探测器研究初探[J]. 红外技术,2007,29(10):563-566.

- [3] Zhao Yang, Gao Shengjiu. Design of multi-function infrared image source system based on FPGA[J]. Laser & Infrared, 2008, 38(11):1106-1109. (in chinese) 赵杨,高升久. 基于 FPGA 的多功能红外图像源系统设计[J]. 激光与红外, 2008, 38(11):1106-1109.

- [4] Zhu Yuanyuan, Huang Zhigang. Infrared signal simulator based on high speed and high accuracy D/A[J]. Journal of telemetry, tracking and command, 2007, 28(2):37 41. (in chinese) 朱元元, 黄智刚. 基于高速高精度 D/A 的红外信号模拟器实现[J]. 遥测遥控, 2007, 28(2):37 41.

- [5] Jiang Xuesong, Wu Yuchun. Design example and emluator of VHDL[M]. Beijing: Publishing House of Mechanical Industry, 2007. (in Chinese) 姜雪松,吴钰淳. VHDL设计实例与仿真[M]. 北京:机械工业出版社,2007.