文章编号:1001-5078(2025)03-0388-07

• 红外材料与器件 •

# 一款适用于高速读出电路的锁相环设计

方 凯<sup>1,2</sup>,董瑞清<sup>2</sup>,李敬国<sup>2</sup> (1. 山东大学,济南 250000;2. 华北光电技术研究所,北京 100015)

**摘 要:**随着红外探测器系统读出电路的数字化发展,读出电路为保证数字信号的运算、传输和存储等处理的正确进行,对时钟信号的要求越来越高。本文基于综合性能良好的电荷泵锁相环结构设计了一款高速时钟信号产生电路,实现在晶振输入 20 MHz 参考时钟信号的条件下,锁相环快速锁定并稳定输出一个 640 MHz 低噪声高速时钟信号。本设计基于 SMICO. 18 μm 工艺,仿真结果表明:在电源电压 1.8~V~ 下,总功耗小于 5~mW,锁相环锁定后的控制电压纹波保持在  $500~\mu V$ 以内,锁定时间为  $4~\mu s$ ,相位噪声小于 -99~dBc/Hz@1MHz,时钟抖动小于 5~ps。

关键词:ROIC;电荷泵锁相环;高速时钟信号

中图分类号:TN215;O436 文献标识码:A **DOI**:10.3969/j.issn.1001-5078.2025.03.010

# A phase-locked loop design for high-speed readout circuits

FANG Kai<sup>1,2</sup>, DONG Rui-qing<sup>2</sup>, LI Jing-guo<sup>2</sup>

(1. Shandong University, Jinan 250000, China; 2. North China Research Institute of Electro-Optics, Beijing 100015, China)

Abstract: With the digital development of readout circuits in infrared detector systems, the requirements for clock signals in readout circuits are becoming increasingly stringent to ensure accurate processing of digital signals, including computation, transmission, and storage. In this paper, a high-speed clock signal generation circuit based on a charge pump phase-locked loop structure with excellent comprehensive performance is designed to achieve fast locking and stable output of a 640 MHz low-noise high-speed clock signal under the condition of a 20 MHz reference clock signal from the crystal oscillator. The designed is based on SMIC 0. 18 $\mu$ m process, and the simulation result shows that total power consumption is less than 5 mW at 1.8 V power supply, the control voltage ripple after the phase-locked loop is kept within 500  $\mu$ V, the locking time is 4 $\mu$ s, the phase noise is less than -99 dBc/ Hz@ 1MHz, and the clock jitter is less than 5 ps.

Keywords: ROIC; charge pump phase-locked loop; high speed clock signal

#### 1 引言

数字化红外焦平面读出电路是目前重要的研究和发展方向,随着焦平面器件的发展和阵列规模不断增长,读出电路芯片内部需要高速时钟信号,以保证高工作频率处理和传输更多更复杂的数字数据信息。由于读出电路处于77 K 超低温环境下,直接外接高速时钟信号会导致芯片内部数

据处理和传输不稳定等各种不良结果。而通过片上集成锁相环不仅可以使整个读出电路芯片外部在统一的低频时钟控制下工作,避免了多信号接入带来的串扰,并且在超低温环境下产生的高速时钟信号具备噪声低,稳定性强的特点,可以被广泛应用于读出电路内部各种不同模块单元,如低压差分信号(LVDS)接口电路、时间-数字转换电

作者简介:方 凯(1999-),男,硕士,主要从事红外读出电路设计。E-mail:fangk\_12309@163.com

通讯作者:李敬国(1976-),男,硕士,高级工程师,主要从事红外焦平面读出集成电路输入级以及信号处理电路的研制工作。

E-mail:lijg@live.com

收稿日期:2024-07-10;修订日期:2024-08-25

路(TDC)等,是解决读出电路未来数字化发展对 高速时钟信号需求的最佳方案。

本文设计了一款高性能的锁相环,在77 K 超低温环境下将读出电路外部低频时钟信号稳定倍频,输出高速时钟信号。通过仿真验证,该锁相环的锁定时间、相位噪声,时间抖动、功耗等技术指标均满足红外焦平面读出电路系统的要求,表现出了良好的性能。

#### 2 电荷泵锁相环系统分析

# 2.1 电荷泵锁相环工作原理

电荷泵锁相环基本结构如图 1 所示,由鉴频鉴相器(PFD)、电荷泵(CP)、低通滤波器(LPF)、压控振荡器(VCO)和分频器(DIV)五个模块组成。

图 1 电荷泵锁相环基本框图

Fig. 1 Basic block diagram of CPPLL

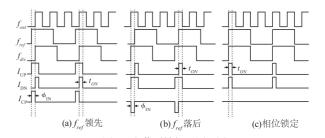

其工作原理可以用图 2 的时序来解释,以分频器的分频比 N = 2 为例,其中  $\phi_{\text{IN}}$  是参考时钟( $f_{\text{ref}}$ ) 和分频器反馈时钟( $f_{\text{div}}$ )之间的输入相位误差。如图 2(a)所示,当 $f_{\text{ref}}$  领先 $f_{\text{div}}$ , $\phi_{\text{IN}}$ 为正时,鉴频鉴相器检测到  $\phi_{\text{IN}}$ ,电荷泵产生正电流脉冲  $I_{\text{CP}}$  为 LPF 充电,从而增加振荡器输出频率( $f_{\text{veo}}$ )以降低  $\phi_{\text{IN}}$ 。如图 2(b)所示,当 $f_{\text{ref}}$  落后 $f_{\text{div}}$ , $\phi_{\text{IN}}$  为负,则电荷泵产生负电流脉冲  $I_{\text{CP}}$  对低通滤波器(LPF)进行放电,从而减小 $f_{\text{veo}}$ ,以减小  $|\phi_{\text{IN}}|$ 。如图 2(c)所示,当参考

时钟与分频器反馈时钟同频同相时, $\phi_{IN}$  保持为零,电荷泵无电流输出,压控振荡器的控制电压保持稳定,锁相环进入锁定状态,锁相环最后稳定输出 N 倍的输入参考时钟信号( $f_{out} = N \times f_{ref}$ )[1]。

图 2 电荷泵锁相环原理图

Fig. 2 Schematic diagram of CPPLL

## 2.2 电荷泵锁相环噪声分析

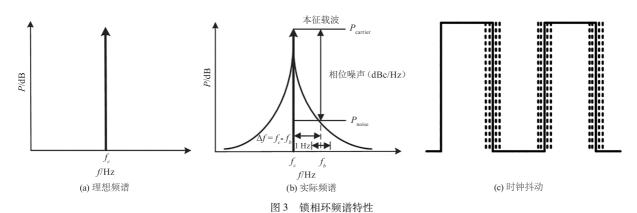

锁相环理想的输出信号是一个纯净的正弦波或者方波信号,如图 3(a)所示在输出频谱表现为一个单独的频谱脉冲。实际的锁相环电路中由于存在一些非理想效应,会导致电路中产生噪声,对锁相环的输出信号产生一定的影响,主要的表现形式为相位噪声和时间抖动。相位噪声是锁相环在频域描述时钟信号不确定性的重要参数,如图 3(b) 所示,该参数定义为距离载波频率  $f_c$  一定频偏  $\Delta f$  处,单位带宽内的噪声功率与载波信号功率的比值,具体计算方法如下式所示,单位为 dBc/Hz:

$$L_{\phi}(\Delta f) = 10\log[P_{\text{noise}}(f_{b})/P_{\text{carrier}}(f_{a})] \tag{1}$$

时钟抖动指时钟周期的边沿与理想值之前的偏差,是锁相环在时域描述时钟信号不确定性的重要参数,如图 3(c)给出了时钟抖动的示意图。时钟抖动和相位噪声是描述锁相环噪声这同一现象的不同参量,在设计锁相环时一般会根据这两种指标来反映锁相环的输出信号的噪声性能<sup>[2]</sup>。

Fig. 3 Frequency spectrum of PLL

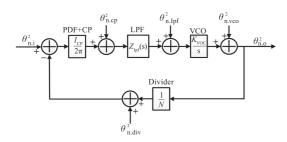

因为目前仍然没有软件可以直接测量出锁相环整体的相位噪声,本文先是通过分析锁相环各个模块电路的噪声特性,建立了锁相环线性噪声模型,如图 4 所示。再根据该模型计算得到如表 1 所示的各模块噪声与锁相环整体输出噪声之间的噪声传递函数,并完成数学建模。最后分别将各个模块电路进行仿真得到的相位噪声实际数据加载到该数学模型中,计算得到锁相环系统整体相位噪声。时钟抖动可以通过对锁相环输出时钟进行周期性采样得到的眼图直观测量,具有一定参考价值。

图 4 电荷泵锁相环线性噪声模型 Fig. 4 Linear noise model of CPPLL

图中  $I_{CP}$  为充放电电流, $Z_{lpf}(s)$  表示为低通滤波器 s 域传递函数, $K_{veo}$  为压控振荡器的灵敏度,单位为  $rad/(s \cdot V)$ 。

表 1 电荷泵锁相环各模块噪声传递函数

Tab. 1 Phase noise transfer function of each module of CPPLL

| 噪声源        | 噪声传递函数                                           |                                                                              | 噪声特性 |

|------------|--------------------------------------------------|------------------------------------------------------------------------------|------|

| PFD/CP 噪声  | $	heta_{	ext{n. o}}(s)/i_{	ext{cp}}(s)$          | $\frac{2\pi}{I_{\rm cp}} \cdot \frac{NH_{\rm open}(s)}{1 + H_{\rm open}(s)}$ | 低通   |

| LPF 噪声     | $\theta_{	ext{n. o}}(s) / v_{	ext{lpf}}(s)$      | $\frac{K_{\text{vco}}}{s} \cdot \frac{1}{1 + H_{\text{open}}(s)}$            | 带通   |

| VCO 噪声     | $\theta_{\text{n. o}}(s)/\theta_{\text{vco}}(s)$ | $\frac{1}{1 + H_{\text{open}}(s)}$                                           | 高通   |

| Divider 噪声 | $\theta_{\text{n. o}}(s)/\theta_{\text{div}}(s)$ | $-\frac{NH_{\text{open}}(s)}{1+H_{\text{open}}(s)}$                          | 低通   |

电荷泵锁相环的开环传递函数  $H_{\text{open}}(s)$ ,如下式所示:

$$H_{\text{open}}(s) = \frac{I_{\text{CP}}K_{\text{veo}} Z_{\text{lpf}}(s)}{2\pi Ns}$$

(2)

分别用  $\theta^2$ <sub>i</sub> 和 H(s)<sub>i</sub> 来表示各模块的等效相位 噪声和噪声传递函数,综上可以计算出总的输出相 位噪声  $\theta^2$ <sub>n.o.</sub>,如下式所示:

$$\theta^{2}_{\text{n.o}} = \sum_{i=1}^{n} \theta^{2}_{i} |H(s)_{i}|^{2}$$

(3)

# 3 电荷泵锁相环各模块设计

## 3.1 鉴频鉴相器

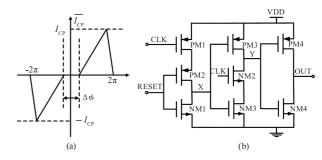

三态门鉴频鉴相器结构如图 1(PFD) 所示,一般包括两个 D 触发器、一个逻辑与门和一个延时单元。 D 触发器的 D 输入信号接高电平置 1,用以检测输入信号的上升沿并输出,检测到参考时钟信号与分频器反馈信号的上升沿之间的时间差即表示为这两个信号的相位差。理想的线性鉴相范围为  $-2\pi \sim 2\pi$ ,而实际上当鉴定的相位差小于一定范围时,电荷泵会因为开关打开的时间过小而无法正常充放电,该开关时间称为为鉴相死区,如图 5(a) 所示。

为了提高鉴频鉴相器的鉴相速度和范围并尽量减小鉴相死区,本文使用了逻辑简结构单且短延时路径的真单相时钟(TSPC)结构的 D 触发器,如图 5 (b)所示。通过在 77K 环境下仿真对 PFD 发现,该结构的应用使得在不添加延时单元对鉴相死区进行消除的情况下,鉴相死区也仅为 10 ps,整体鉴相范围可以达到 - 356°~356°,鉴相误差为 2%,满足系统要求。

图 5 TSPC 结构 D 触发器

Fig. 5 D flip-flop of true single-phase clock structure

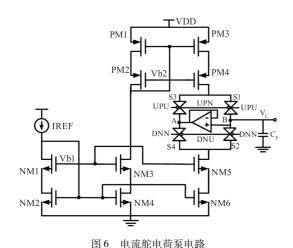

#### 3.2 电荷泵

本文设计了一种改进的电流舵电荷泵结构,如图 6 所示。该电路对电荷泵中实际存在的电流失配、时钟馈通、电荷注入、电荷共享等非理想特性<sup>[3]</sup>进行了很好的抑制,使得在 LPF 上产生的周期性电压纹波很小,极大程度提升了锁相环输出信号质量。

四个传输管开关 S1-S4 组成了电流舵结构,有 效解决了 MOS 管开关会造成的时钟馈通效应的同时,也提高了电荷泵开关的速度,从而降低了锁相环 产生高速时钟信号的建立时间。

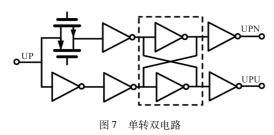

开关的闭合与断开由 UP 和 DN 信号经过如图

7 所示的单转双电路得到的 UPU、UPN、DNU 和DNN 信号控制。以 UP 信号为例: UP 信号分别经过一级传输管和三级反相器得到反相信号 UPN,经过四级反相器得到同相信号 UPU。该些级联反相器的尺寸在设计时逐级成倍增加,既提高了 UPN 信号的驱动能力,又可以通过将 UPU 信号链的第二级反相器输入输出端和 UPN 信号链第三级反相器输入输出端交叉耦合,以保证 UPU 信号与 UPN 的同步输出,减小了开关时间失配。

S1 和 S2 同时闭合时,负载电容和上下电流源 MOS 管源漏电容中的电荷量会重新分布而导致共享效应,该效应会导致控制电压跳变出现毛刺并将杂散通过压控振荡器引入到输出信号。设计时为了消除电荷共享效应,在电流舵两边支路开关之间加入了一个单位增益放大器,在放大器的钳位作用下,B点电压可以在 S1 和 S2 闭合时保持 A 点电压一致,防止了控制电压 因为电荷的重新分布所引起的波动,有效解决了电荷共享效应<sup>[4]</sup>。

F: 6.0 . . . . . 1

Fig. 6 Current steering charge pump

Fig. 7 Single-end to double-end circuit

为确保电荷泵输出端的工作电压满足压控振荡器对应输出频率要求的控制电压范围,在 tt 工艺角、77 K 的条件下对该电荷泵进行仿真,仿真结果显示充放电电流误差小于 1 μA 的输出电压范围为

0.4~1.6 V,满足压控振荡器的控制电压范围要求,可以锁定到指定频率。

#### 3.3 低通滤波器

因此本文在设计时选择如图 1(LPF) 所示的二阶 RC 低通滤波器。该滤波器不仅可以将电荷泵输出电流转换为压控振荡期所需的控制电压,将控制电压中高频噪声过滤掉,并且通过分析锁相环系统开环传递函数可知,低通滤波器中 RC 的取值是锁相环系统能否稳定工作的关键<sup>[5]</sup>。锁相环稳定性和 RC 取值关系的分析如下:

二阶 RC 低通滤波器的传递函数如下式所示:

$$Z_{\rm lpf}(s) = \frac{1 + sR_1C_1}{s[R_1C_1C_2s + C_1 + C_2]} \tag{4}$$

将公式(4)代入公式(3)可得锁相环的开环传 递函数如公式(5)所示:

$$H_{\text{open}}(s) = \frac{I_{\text{CP}}K_{\text{vco}}}{2\pi N} \cdot \frac{1 + sR_1C_1}{s2[R_1C_1C_2s + C_1 + C_2]}$$

(5)

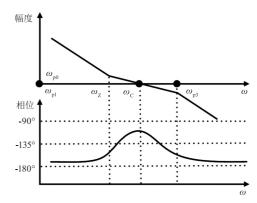

该开环传递函数表明锁相环系统存在一个零点 $\omega_z$ ,两个在原点处的极点 $\omega_{p1}$ , $\omega_{p2}$ 和一个非零极点 $\omega_{p3}$ ,其波特图如图 8 所示。

图 8 锁相环波特图

Fig. 8 Bode diagram of PLL

锁相的稳定性与相位裕度存在直接的关系,根据对波特图的分析可知,当相位的最大值取在环路带宽 $\omega$ 。时所得到的相位裕度最大。该开环传递函数在任意角频率的相位裕度如公式(6)所示:

$$\phi_m = \tan^{-1} \frac{\omega_c}{\omega_r} - \tan^{-1} \frac{\omega_c}{\omega_{\rho 3}}$$

(6)

如果用 b 表示  $C_1$  和  $C_2$  的比值  $b = C_1/C_2$  ,可以得到相位裕度关于 b 的表达式,如下式所示:

$$\phi_m = \tan^{-1} \left[ \frac{1}{2} \left( \sqrt{b+1} - \frac{1}{\sqrt{b+1}} \right) \right]$$

(7)

使用最大相位裕度法,可以得到 $R_1$ 、 $C_1$ 、 $C_2$  关于

b的表达式,如公式(7)~(9)所示:

$$C_2 = \frac{I_{\rm CP} K_{\rm veo}}{2\pi N \,\omega_c^2} \cdot \frac{1}{\sqrt{b+1}} \tag{8}$$

$$C_1 = \frac{I_{\rm CP} K_{\rm vco}}{2\pi \omega_c^2} \cdot \left(\frac{b}{\sqrt{b+1}}\right) \tag{9}$$

$$R_1 = \frac{2\pi N\omega_c}{I_{\rm CP}K_{\rm vco}} \cdot (1+b) \tag{10}$$

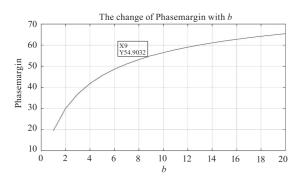

为了选择合适的相位裕度,以确定合适的  $R_1$ 、 $C_1$ 、 $C_2$  取值,使用 MATLAB 对公式(7)进行仿真,仿真结果如图 9 所示。

图 9 相位裕度关于 b 值的 MATLAB 仿真 Fig. 9 Simulation of phase margin about b

本文选取锁相环系统在相位裕度为 54.9 时的 b 值, b =9, 并根据据读出电路对高频时钟信号的要求, 确定了锁相环系统带宽为 1.5 MHz。以上数据代入公式(8)~(10)计算得到二阶低通滤波器电阻电容各参数分别为:  $R_1$  =9308  $\Omega$ ,  $C_1$  = 36.05 pF,  $C_2$  =4 pF。

## 3.4 压控振荡器

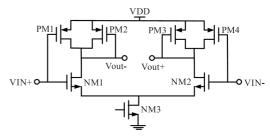

压控振荡器电路可以实现不同电压控制下,输出不同频率的功能,是锁相环中最重要的模块,考虑到读出电路所需的高速时钟信号频率在 GHz 以内,选择面积小,易集成,成本低的环形振荡器结构<sup>[6]</sup>。环形振荡器单元电路如图 10 所示,整体采用可以消除电源与衬底共模噪声的全差分结构,通过控制电压调节尾电流源大小来改变振荡频率,PM2 和 PM3 采用二极管连接保持恒定的负载增加了压控振荡器的线性度,PM1 和 PM4 和分别连接输入端以实现振荡器输出的全摆幅。通过四级该单元振荡电路构成回路,最后仿真显示振荡器频率范围可以从 50 MHz 到 850 MHz,满足高速时钟信号频率要求。

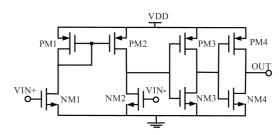

对于该压控振荡器,因为其产生的周期波形不 是标准的正弦波,且为双端输出,所以添加了一个如 图 11 所示的整形电路对振荡器输出信号波形进行 整形,将双端输出信转换为分频器可以分频处理的占空比50%的单端信号。

图 10 环路振荡器单元电路结构

Fig. 10 Loop oscillator unit circuit structure

图 11 压控振荡器输出波形整形电路

Fig. 11 Level shift circuit for voltage controlled oscillator output

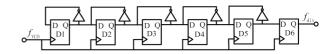

# 3.5 分频器

本文锁相环将 20 MHz 的参考时钟倍频到 640 MHz,采用的是一个分频比 N = 32 的整数分频器,分频器结构如图 12 所示,由 6 个 D 触发器和 5 个反相器构成。其中 D1 ~ D5 各自搭配一个反相器组成二分频器,然后串联起来完成 32 分频的功能。这种串联分频延时链的结构虽然结构简单,但是从输入时钟信号到输出时钟信号的延时增大了,这会导致延时和噪声的积累。于是本文在分频器的末端加上了一个 D 触发器(如图 12(D6))进行重新定时,从而使得分频器的输出噪声仅包含这一个重新定时 D 触发器的噪声,分频器相位噪声被显著抑制[<sup>77</sup>]。

图 12 分频器结构框图

Fig. 12 Structure diagram of divider

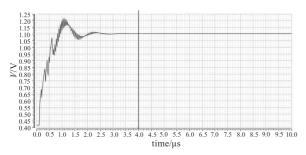

#### 4 锁相环环路仿真

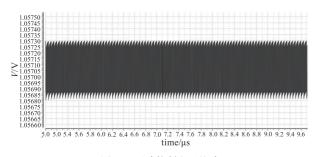

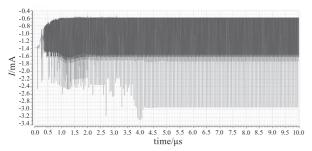

本文设置读出电路仿真环境为 - 150 TT 1.8V, 对锁相环各项设计指标参数进行仿真,得到图 13 所示的控制电压波形,图 14 所示的环路锁定后控制电压纹波和图 15 所示的锁相环整体功耗图。

图 13 锁相环控制电压波形

Fig. 13 Controlled voltage waveform of phase locked loop

图 14 环路控制电压纹波

Fig. 14 Loop control voltage ripple

图 15 锁相环整体功耗

Fig. 15 Total power consumption of phase-locked loop

该锁相环的锁定时间为 4 μs,锁定时控制电压为 1.057 V,控制电压纹波很小,稳定保持在 500 μV 以内,锁相环总功耗为 4 mW。可以从仿真结果看出,设计的锁相环整体性能良好,具有锁定时间快、控制纹波小,功耗小的优点。

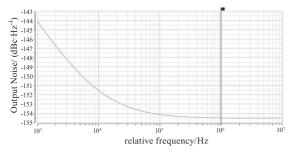

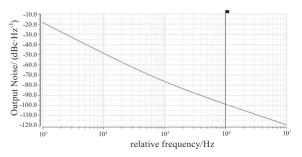

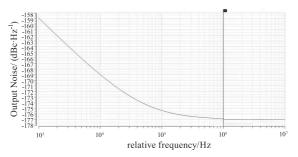

最后通过 spectre 仿真得到如图 16、图 17、图 18 所示的锁相环环路中的各模块的相位噪声。

图 16 鉴频鉴相器和电荷泵噪声曲线

Fig. 16 Noise curve of PFD and CP

图 17 压控振荡器相位噪声曲线

Fig. 17 Noise curve of VCO

图 18 分频器相位噪声曲线

Fig. 18 Noise curve of divder

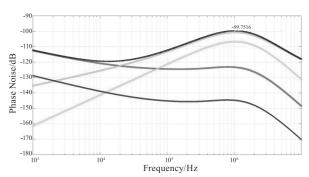

输入参考时钟信号一般由晶振提供,其相位噪声为带内相位噪声,相比于其他模块的相位噪声一般忽略不计。低通滤波器的相位噪声主要来源于电阻  $R_1$  产生的热噪声。根据以上通过仿真得到的三部分相位噪声数据再加上低通滤波器的电阻热噪声数据,使用已完成的数学模型对这些噪声拟合,可以得到锁相环总相位噪声曲线,如图 19 所示。锁相环在频偏1 MHz 的相位噪声为 - 99.75 dBc/Hz,满足高速读出电路对时钟信号的相位噪声要求。

图 19 总相位噪声曲线

Fig. 19 Phase noise curve of phase-locked loop

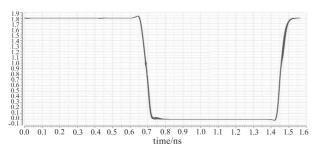

除了相位噪声,时钟抖动作为锁相环在时域描述信号不确定性的参数,也是体现锁相环输出的高速时钟信号质量的重要指标。一般可以通过采样输出信号多周期形成的眼图来确定时钟抖动的大小。图 20 为 − 150 ℃ TT 1.8 V 仿真条件下,通过对锁

定后的 640 MHz 高速时钟信号进行差分采样得到的眼图,采样 1250 个周期,可以得知改输出信号的时钟抖动为 4.14 ps。

图 20 输出信号眼图

Fig. 20 Eye diagram of phase-locked loop output signal

## 5 结 论

本文为满足读出电路电路数字化发展对高速时钟的需求,设计了一款适用于高速读出电路的高性能锁相环,基于 SMICO. 18 μm 工艺,将读出电路20 MHz低频工作时钟信号倍频,稳定输出一个640 MHz低噪声、低抖动的高速时钟信号。最终实现高速时钟信号的建立时间仅为 4 μs,功耗小于5 mW,相位噪声为 – 99.75 dBc/Hz@1 MHz,时间抖动为 4.14 ps。通过使用该锁相环设计产生的高速时钟信号,读出电路的读出速率和红外探测器性能可以得到有效提高,为未来读出电路数字化及大面阵发展对高速时钟信号的需求提供了有力的技术保障。

# 参考文献:

- [1] Hao Zhang. Cmos analog and mixed-signal phase-locked loops:an overview [J]. 半导体学报(英文版),2020,41 (11):15-32.

- [2] YU ZHAO, BEHZAD RAZAVI. Phase noise integration limits for jitter calculation [C]//2022 IEEE International Symposium on Circuits and Systems (ISCAS 2022), 2022: 1005 – 1008.

- [3] DONGIN KIM, SEONGHWAN CHO. A supply noise insensitive PLL with a Rail-to-rail swing ring oscillator and a wideband noise suppression loop[C]//2017 Symposium on VLSI Circuits, 2017:134 135.

- [4] ABDULAZIZ, MOHAMMED, FORSBERG, et al. A 10 mW mm-wave phase-locked loop with improved lock time in 28 nm FD-SOI CMOS [J]. IEEE Transactions on Microwave Theory and Techniques, 2019,67(4):1588-1600.

- [5] LEVANTINO, S., MARZIN, G., SAMORI, C., et al. A wideband fractional-N PLL with suppressed charge-pump noise and automatic loop filter calibration [J]. IEEE Journal of Solid-State Circuits, 2013, 48 (10):2419 - 2429.

- [6] NITIN KUMAR, MANOJ KUMAR. Design of CMOS-based low-power high-frequency differential ring VCO

[J]. International journal of electronic electronic electronic (2):143-153.

- [7] WENFENG LOU, XIAODONG LIU, PENG FENG, et al. An integrated 0. 38 – 6 GHz, 9 – 12 GHz fully differential fractional-N frequency synthesizer for multi-standard reconfigurable MIMO communication application [J]. Analog Integrated Circuits and Signal Processing, 2014, 78 (3):807 – 817.